# **Performance Modeling of Virtualized Custom Logic Computations**

Michael J. Hall, Roger D. Chamberlain Department of Computer Science and Engineering

Supported by NSF Grant CNS-0931693 and Exegy, Inc.

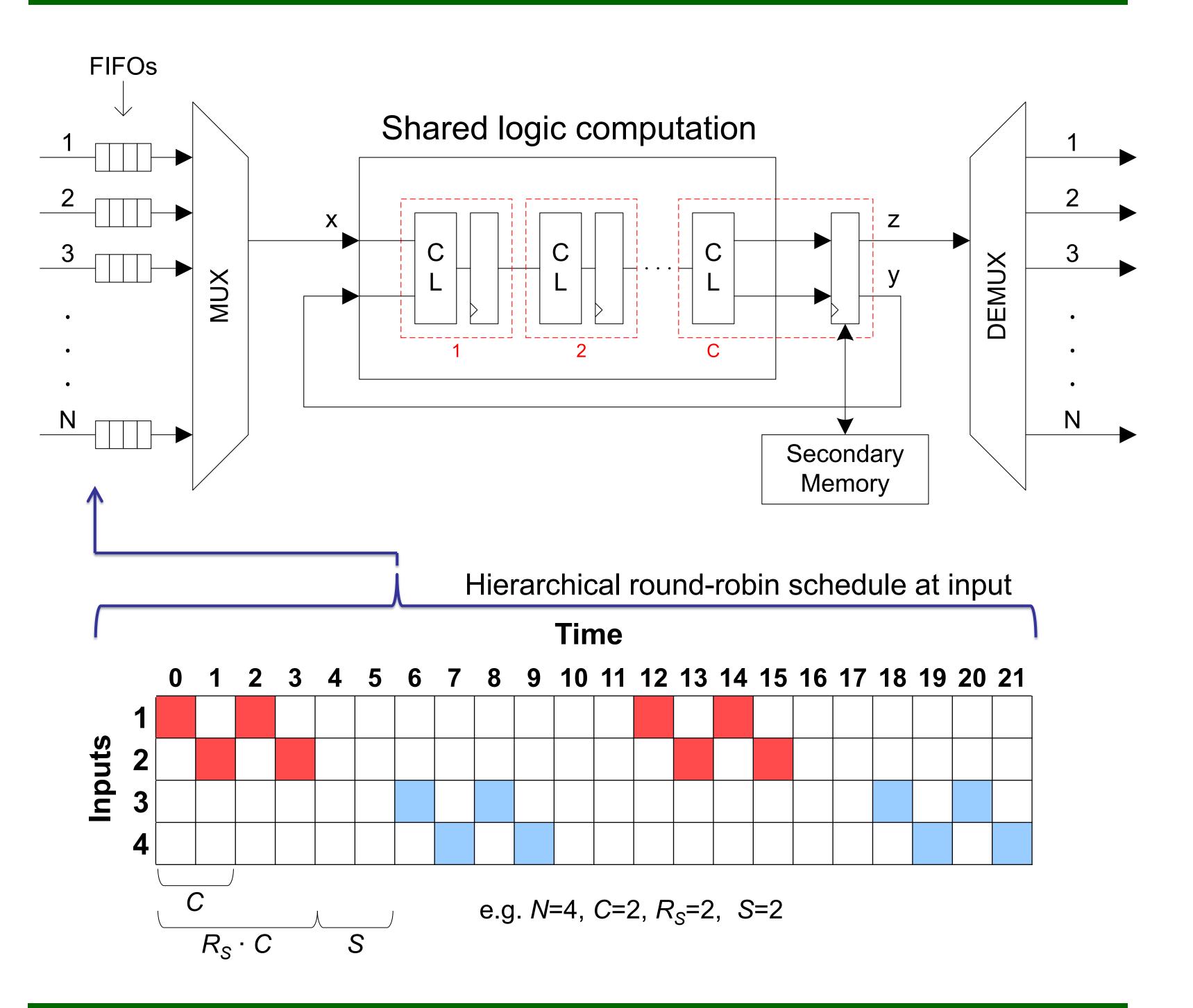

## Virtualized Logic Computation

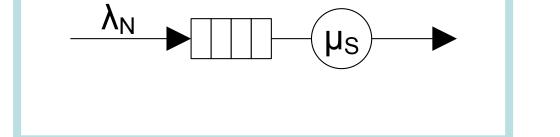

## **Queueing Model**

#### Model definition:

Tput, Latency, Occupancy =  $f(Circuit, Tech, C, N, S, R_S, \lambda)$

Scheduling period (number of rounds of C contexts that execute

| Variable | Definition                                                     |

|----------|----------------------------------------------------------------|

| Circuit  | Logical circuit description (e.g. written in Verilog or VHDL)  |

| Tech     | Target technology (e.g. FPGA or ASIC)                          |

| С        | Pipeline depth (fine-grain contexts)                           |

| N        | Total number of contexts (requires secondary memory if $N>C$ ) |

| S        | Cost of a context switch (for secondary memory)                |

| D        | Schoduling pariod (number of rounds of C contexts that execute |

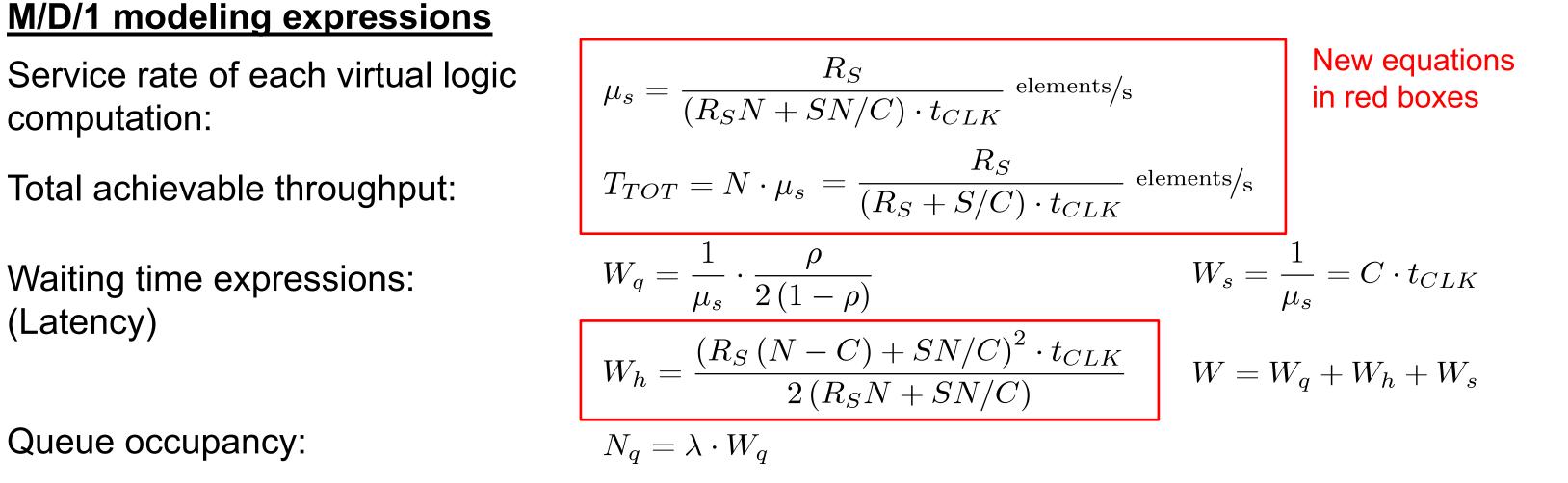

computation:

(Latency)

before context-switching to secondary memory)

Arrival rate (e.g. data elements per second)

#### Calibration

| CL     | - CL -     | CL | CL             |

|--------|------------|----|----------------|

| <br>X₁ | <b>X</b> 2 |    | X <sub>C</sub> |

| ariable | Definition                                                                     |

|---------|--------------------------------------------------------------------------------|

| X       | Random variable of stage-to-stage delay for C random samples, $x_1, x_2,, x_C$ |

- Pipeline depth С

- Total comb. logic delay  $t_{CL}$

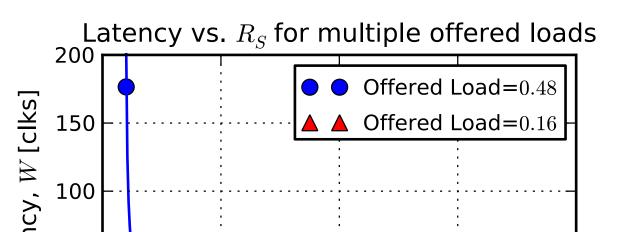

#### **Model Validation**

Queue occupancy:

Offered load is the ratio of aggregate arrival rate to the peak service rate of the system and is equal to  $N \cdot \lambda \cdot t_{CLK}$ .

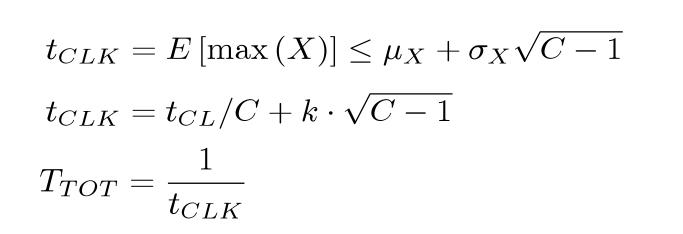

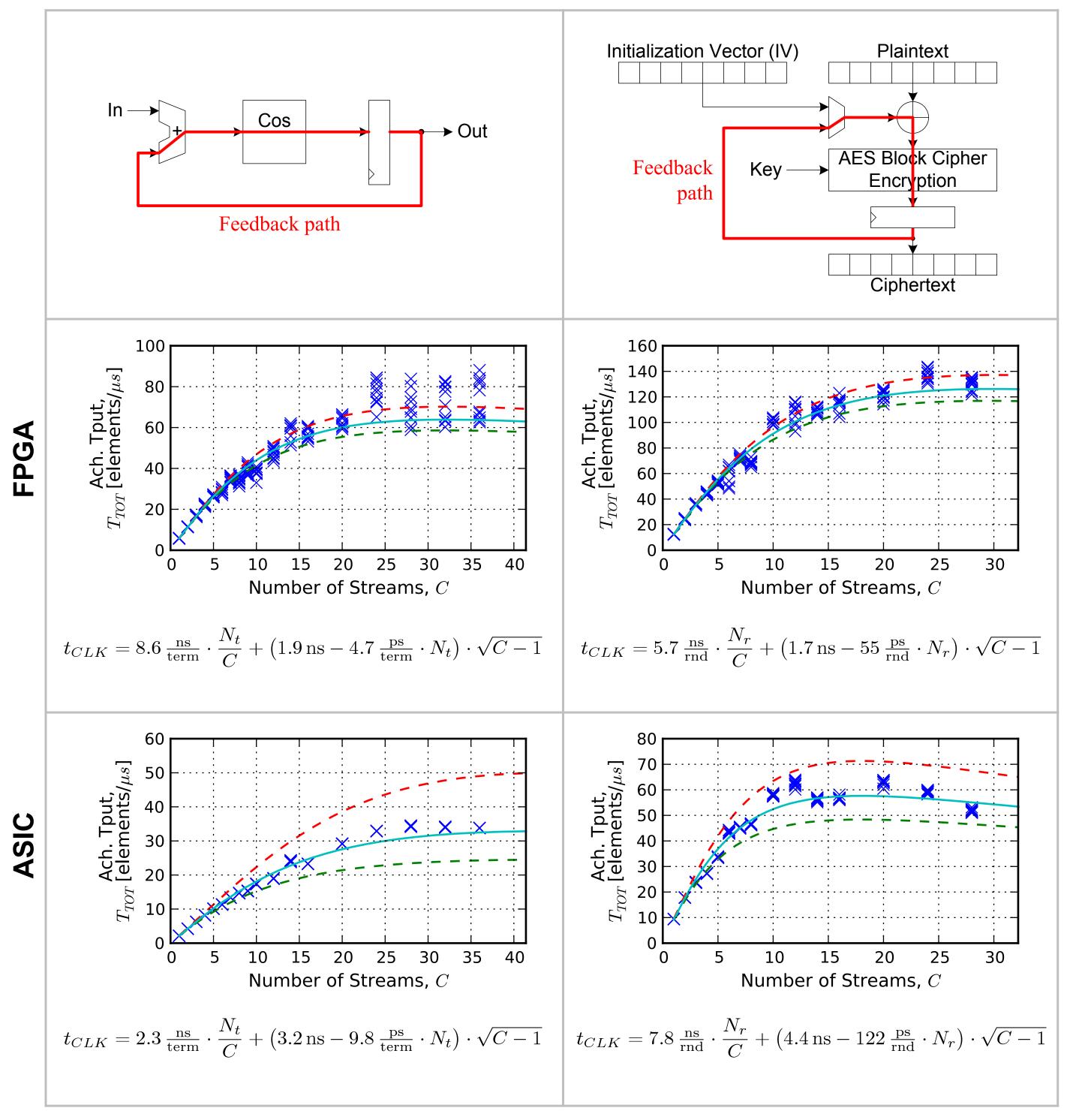

#### Curve fit parameter

Upper bound on t<sub>CLK</sub> from order

statistics:

Clock period sub-model:

$N = 8, C = 4, S = 4, t_{C/K} = 100 \text{ MHz}$

- Points are discrete event simulation

- Curves are analytic expressions

#### Ways to Use the Model and Results

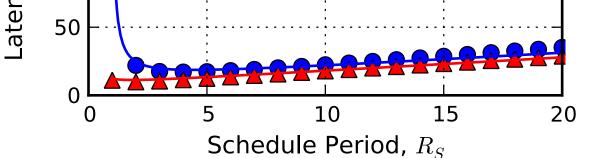

**Example Design - Case 1** Given:

*Circuit*=COS, *Tech*=FPGA, *N*=100, *C*=10, *S*=100, *OL* varies Design Params:  $R_{s}$ Optimize: *FoM=Tput/Latency*

# --- OL=0.001 OL = 0.4

0.4

Offered Load

0.6

8.0

0.2

0.0

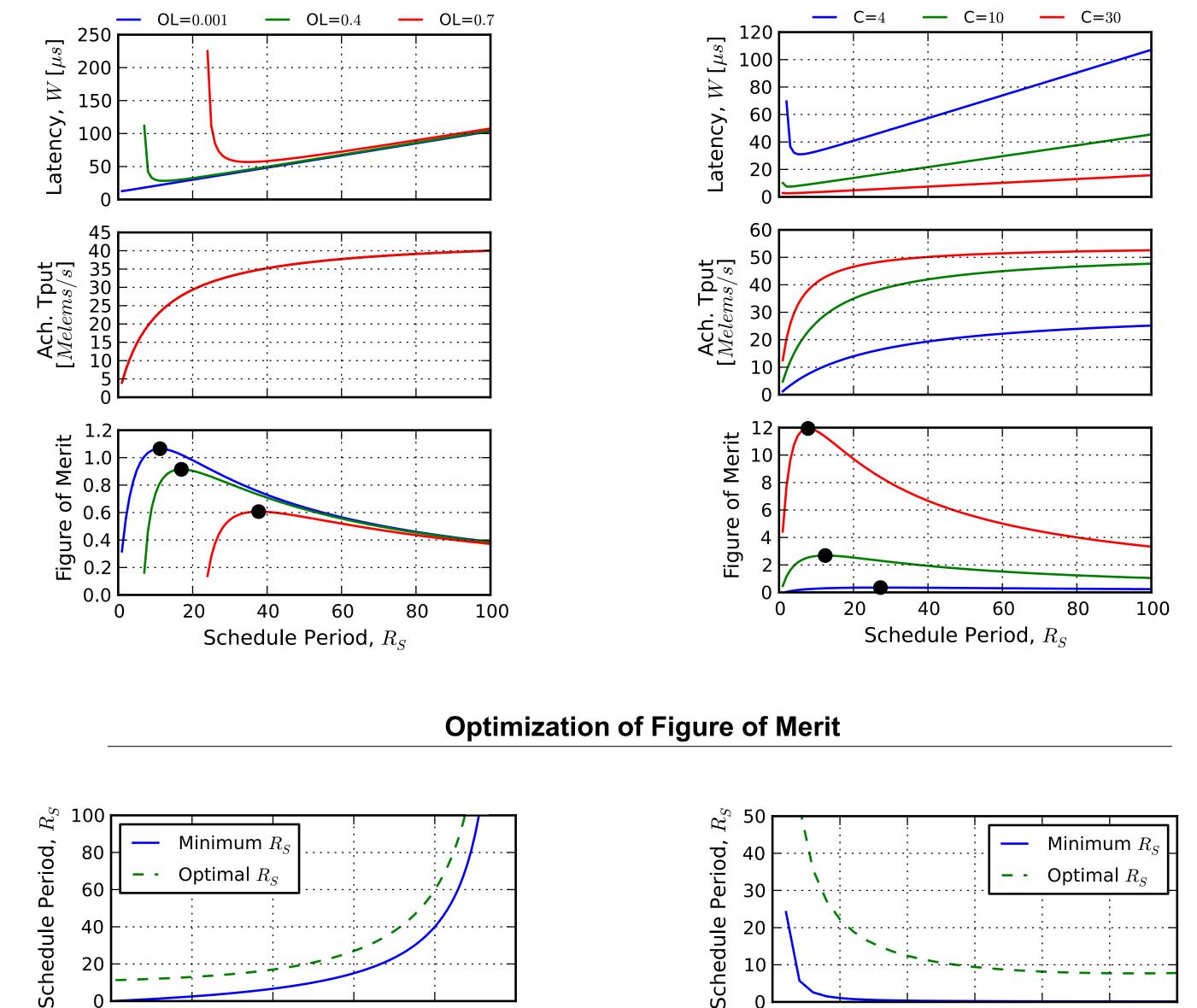

#### **Example Design - Case 2** Given:

• *Circuit*=AES, *Tech*=ASIC, *N*=60, *S*=100, *λ*=30 Kelems/s Design Params:  $C, R_{s}$ Optimize: *FoM=Tput/Latency*

Synthetic Cosine Application with Feedback (20 Taylor-series terms)

**AES Encryption Cipher in CBC Block** Mode (14 fully unrolled rounds)

Schedule

1.0

15 20 25 10 30 5 Number of pipeline stages, C

0